Opal Kelly challenged its experts to create a useful PC-based logic analyzer using an Opal Kelly XEM3001, XEM3005, or XEM3010 (and, optionally, a BRK3005 or BRK3010 breakout board). Very few constraints were placed on the design, but generally:

- Spend no more than one man-day (approximately 8-10 hours) on the project.

- Typical logic analyzer features were suggested, but no firm specification was provided.

- Documentation, code comments, and optional project installers could be completed outside the bounds of the 8-10 hours.

- The project sources will be open-sourced, so any re-used HDL or software will need compatible licensing. The MIT License and Creative Commons License were suggested.

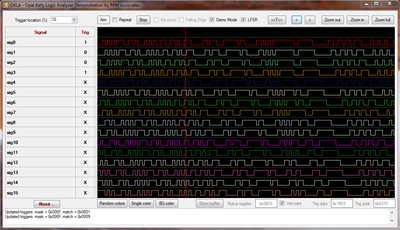

Rainer Malzbender’s Logic Analyzer

- HDL: VHDL

- Software Language: C# + FrontPanel SDK

- Hardware: Opal Kelly XEM3005 and BRK3005

Rainer was able to pull extensively from previous work and built a very functional graphical logic analyzer. He used the BRK3005 and incorporated a simple pseudo-random signal generator to exercise his logic analyzer. When male headers are installed in the BRK3005, several jumpers connect his signal generator to his logic analyzer to easily demonstrate the capabilities.

The user specifies the trigger mechanism using an intuitive 0, 1, or X (don’t care) selection next to each signal name and can even set the trigger position within the full capture buffer.

Download ZIP (795 kiB)

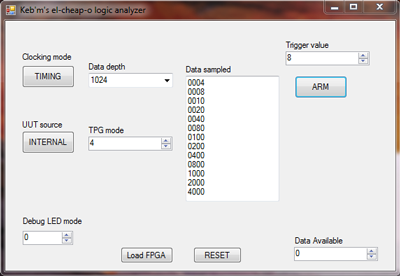

Kevin Smith’s Logic Analyzer

- HDL: VHDL

- Software Language: C# + FrontPanel SDK

- Hardware: Opal Kelly XEM3010 and BRK3010

Kevin Smith decided to use the opportunity to learn a new development environment. The Logic Analyzer in a Day project was his first attempt at C# development. His analyzer has a simple GUI with textual output of the acquired data rather than a waveform view.

Kevin’s VHDL has a few hidden gems that could prove useful to other Opal Kelly developers including extensive Python scripts for command-line build of Xilinx projects as well as a unique way to define endpoints within the FrontPanel framework.

Download ZIP (536 kiB)

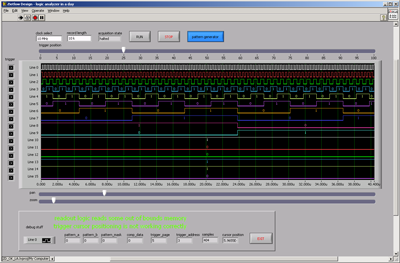

Klaus Zietlow’s Logic Analyzer

- HDL: Verilog

- Software Language: LabVIEW + FrontPanel SDK

- Hardware: Opal Kelly XEM3005 and BRK3005

Klaus is a long-time user of LabVIEW for prototyping complex systems, so it was a natural choice for him to re-use some previous projects to build up his logic analyzer GUI under the demanding one-day timeline. Many Opal Kelly customers use LabVIEW with the FrontPanel SDK, so we were pleased to see an entry take this direction.

Klaus was also the only one of the three to utilize Verilog in his design.

Download ZIP (491 kiB)