Flexible, High Performance FPGA Power Solution Testing using the XEM7320, XEM7350, and FrontPanel

Good power management and power integrity is at the heart of all electronic systems. This is especially true of FPGA based systems where I/O and logic switching speeds are fast and current demands at low voltages can be high. This is further compounded by the flexible nature of FPGAs as device power depends greatly upon not only switching frequency but also the utilization of the FPGA resources. The power distribution system (PDS) must therefore be able to support a wide range of device use cases.

However, while FPGAs present these challenges to the designer they also form the cornerstone to verifying the power solution. One commonly used method to test power solution suitability for an FPGA based solution is to create a test design which clocks at an appropriate speed and also attempts to utilize a significant portion of the FPGA resources.

Developing such a PDS test design also presents its own issues to the development team. The test design has what can be conflicting requirements. To present a high demand on the power solution it needs to utilize as many resources as possible. However, if these resources are judged to be redundant by the synthesis tool they will be optimized out of the design. The development team must therefore create a design which utilizes a significant proportion of the device resources, which cannot be optimised away and do so within a sensible time. The design must also be easily portable to new devices without significant reengineering work. To achieve this, the design uses simple, well supported HDL code structures and avoids use of any vendor-specific IP or primitives, relying on vendor tools to infer the desired resources.

Recently the Opal Kelly engineering team created a reference power supply test design and examined its performance when deployed on both the XEM7350 and XEM7320.

To address the resource utilization issues outlined above, the following techniques were employed:

- Large Linear Feedback Shift Registers (LFSR) used to provide stimulus to DSP resources.

- Simultaneous read and writes to multiple Block RAMs.

- I/O driven via reducing and combining several LFSR / DSP outputs.

One goal of the PDS test design was to ensure no synthesis constraints or attributes were required in the source RTL to prevent synthesis optimization. The engineering team achieved this by XORing several LFSR outputs together to drive a single output connected to a I/O (in this case, an LED). Another technique used to prevent synthesis optimizations of the multiple LFSRs in the design was the use of different seeds for each LFSR. This prevented the removal of LFSRs which could be judged by the synthesis tool to be redundant.

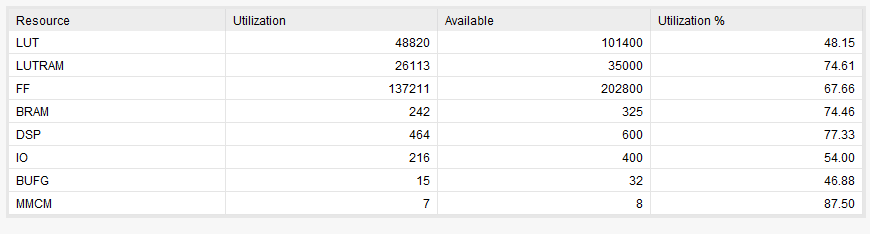

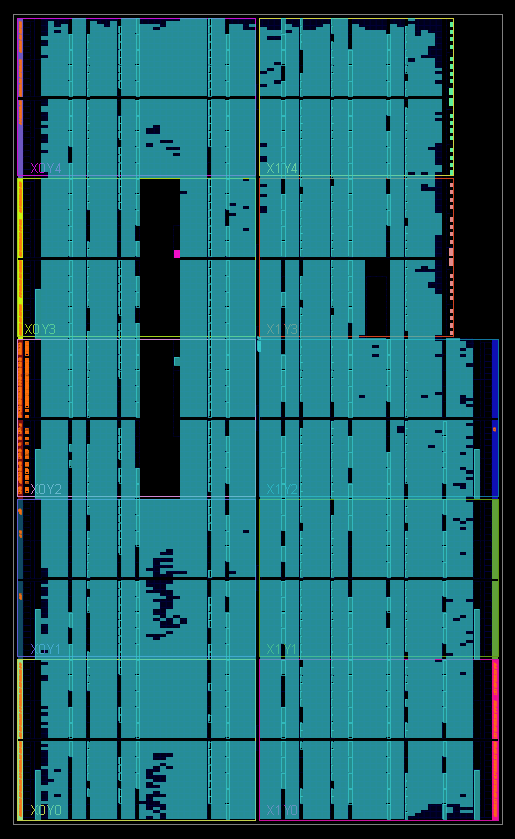

Implementing the reference design in both the XEM7320 and XEM7350 shows the test design achieved the desired resource utilization.

Running the PDS test design on the XEM7320 and XEM7350 demonstrates that the power supply is capable of supporting FPGA designs which are pushing the performance envelope. This ensures that the final module design meets the PDS requirements and the power specification provided by Opal Kelly.

Of the two designs the XEM7350 is a larger design and places more demands on its power supply solution due to the use of a higher-density FPGA. With the PDS test design running, the XEM7350 FPGA draws a current of 7.9A for the FPGA core and has a total board dissipation just under 15W.

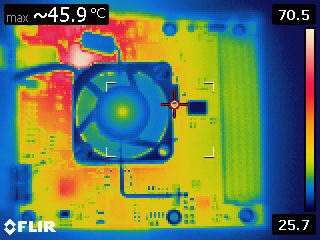

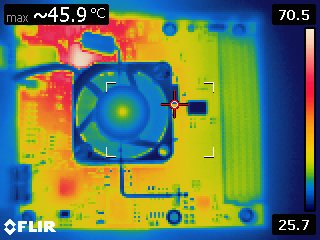

Observing both modules with a thermal imaging camera shows very visibly the effects the PDS test design has on the FPGA and power supply components. It also demonstrates the impact of an effective cooling solution on the junction temperature of the device when under a high load.

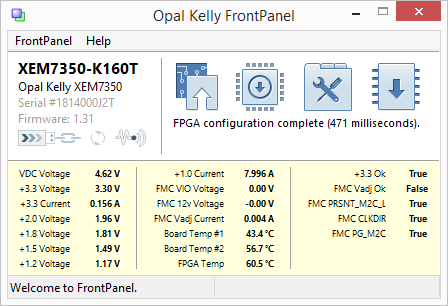

To help understand PDS behavior during operation, the XEM7350 also contains an integrated device sensor readout which can be accessed via FrontPanel. This sensor readout provides the ability to monitor the supply rail voltages and currents along with board and FPGA temperatures. This is very useful to check if voltage rails are collapsing as the current demand increases which could indicate an overload condition on a supply rail.

The PDS test design demonstrates the ease with which a power solution can be verified for an arbitrary FPGA module. For the XEM7350 the ability to integrate FrontPanel allows for not only real time monitoring of the power supply system with ease but also monitoring of the actual application providing prognostics once deployed.

The goal of this project was to create a set of parameterizable modules to generate a defined level of resource utilization inside the FPGA. This set of modules can then be used to quickly construct bitstreams that target specific FPGA densities which may then be used to exercise the power distribution system on an FPGA module and measure its performance characteristics at varying loads in system. The resulting HDL from this project will be used to further test, verify, and improve our product designs so our customers can be confident that our modules will perform well across a wide variety of applications.

Additional Resources

XEM7320 Documentation: https://docs.opalkelly.com/xem7320

XEM7350 Documentation: https://docs.opalkelly.com/xem7350

FrontPanel: https://opalkelly.com/products/frontpanel/