SYZYGY Origin Story (abridged)

No matter how glamorous it may seem, the development and introduction of a new standard to an existing marketplace is not a savory project (see xkcd 927). It’s a period of research, iteration, skepticism, hope, and self-doubt. In the end, the goal is to satisfy some need for some people while accepting the fact that not all needs and not all people will be satisfied. This short blog post briefly explains why we decided to introduce SYZYGY® (pronounced si-zə-jē) as a new standard for FPGA-to-peripheral connectivity.

Customers

As an FPGA integration module manufacturer, we have spent years building products that solve a piece of the hardware puzzle for our customers. While our products often meet most customers needs, inevitably, the market would like that you solve some additional piece of the puzzle that feels like it should be commodity.

The majority of our products end up in custom-built installations as “integration modules”. However, a fair number of applications involve prototypes, one-off projects, or extremely low-volume builds.

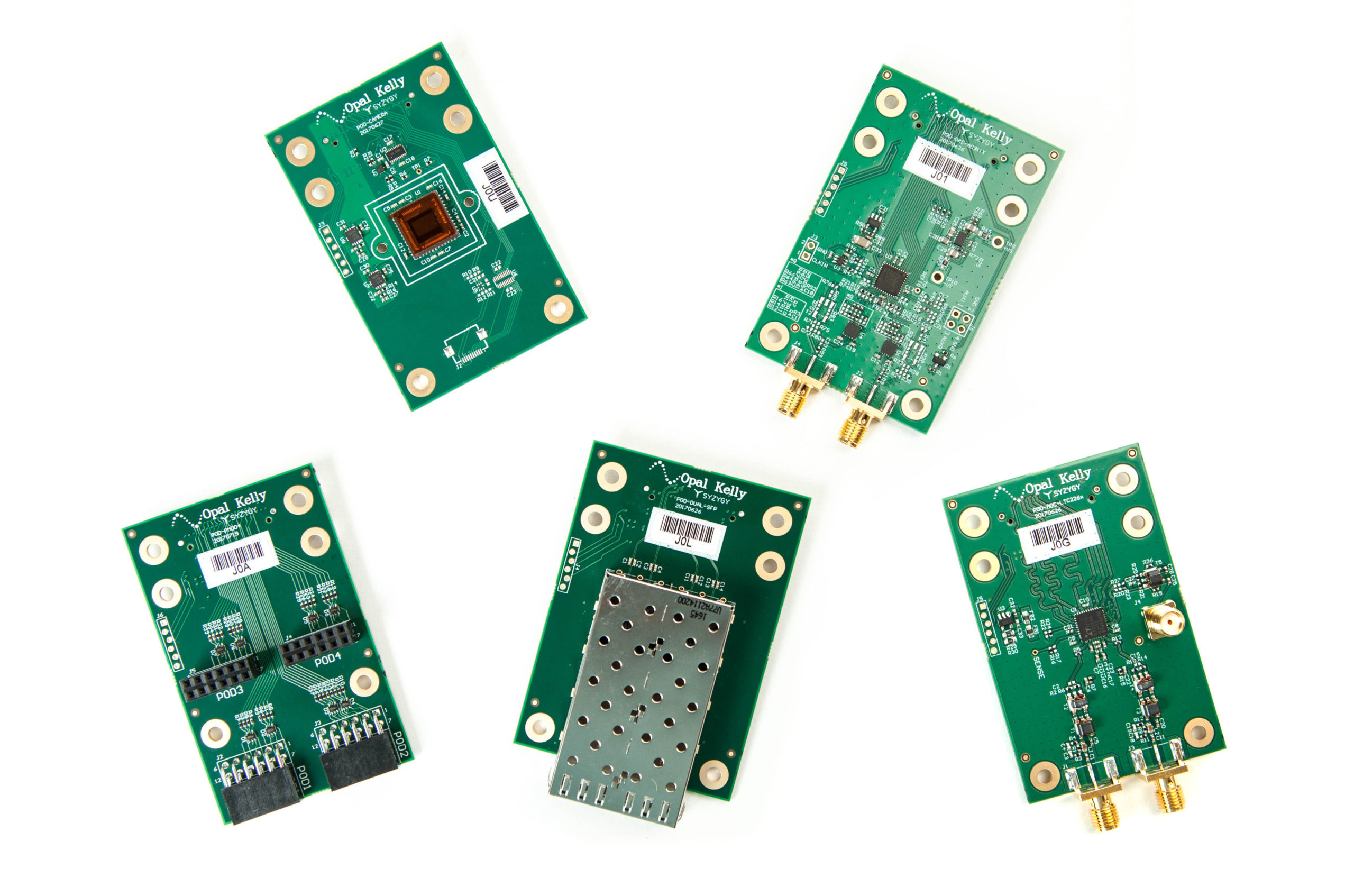

For our customers, the most commonly requested addition is for ADC or DAC devices to our modules. The problem we face is that of finding an appropriate fit for the broad variety of customer applications we served. There are approximately 33,356 DACs, ADCs, and CODECs in the Digi-Key item master. So even if we are ambitious and choose 20 among them, we have presumably left 33,336 unfulfilled demands on the table.

Additionally, our products are often used in evaluation settings such as the Texas Instruments ADS1675REF. While the user experience of this type of eval product is very nice, we feel it would be even better with a standard interconnect so that the device under evaluation can be used with other environments.

In a nutshell, this was the starting premise for the SYZYGY interconnect standard: to provide some connectivity and peripheral ecosystem for development-stage projects.

Motivation and Goals

We had previously been impressed by the Digilent PMOD standard that was introduced at about the time that small, low-cost sensing devices started to proliferate, utilizing simple bus protocols like I2C and SPI. We were also familiar with VITA 57.1 (FMC), a high-performance standard fronted by Xilinx to interface composite (multi-function) peripherals to FPGAs. What we needed to serve our high-performance data acquisition customers was a system with the simplicity and I/O efficiency of PMOD but with the performance of FMC.

SYZYGY is intended for three general categories of applications:

- High-Performance Prototypes

- System Integration and Testing

- Evaluation Systems

Specifically, we established the following requirements:

- FPGA-centric (i.e. not CPU centric like PC-104)

- Device focus: sensing, ADC, DAC, image sensors, SDR

- Moderate pin count for FPGA I/O efficiency and single-function peripherals

- High-performance I/O speeds (50 Mbps to 1 Gbps per pin) supported by the connector

- Ultra-high performance option for transceiver-based peripherals

- VCCO programmable and managed by the carrier to maintain compatibility within the bank

- Cable-capable for devices such as image sensors where some flex is desirable

- Support for securing peripherals to carriers mechanically

Finding a Connector

The first step in our approach was to compile a reasonably comprehensive list of devices we wanted to support with the standard, including specific manufacturer part numbers. This research would provide important guidance on I/O standards, voltage ranges, power consumption, and pin count.

The first step in our approach was to compile a reasonably comprehensive list of devices we wanted to support with the standard, including specific manufacturer part numbers. This research would provide important guidance on I/O standards, voltage ranges, power consumption, and pin count.

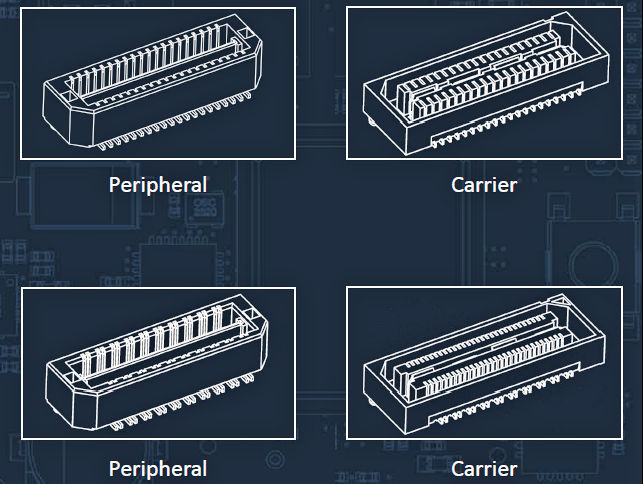

Once the space of device support was determined, we set about making a choice of connector. We had previously used Samtec connectors extensively, but dispensed with any historical bias and considered connectors from several manufacturers. We were particularly interested in finding a commodity connector standard that could be used. This would likely provide a low-cost, multi-source connector that would be readily available and easy for manufacturers to adopt. (Ultimately, a commodity connector could not be found that met our requirements.)

Digilent PMOD peripherals are typically very low cost devices, so the standard is not tolerant of a connector that costs 5x that of the device it supports. We had a higher tolerance for connector cost due to the higher typical cost of the peripheral device (100 MSPS ADCs cost more than temperature sensors), but not quite as high as FMC.

Eventually, we settled on Samtec QSE and QSH connectors. Supply lead time had always been rock steady at 2-3 weeks, cost was stable and reasonable, build quality was consistent, technical specification and documentation were excellent, and the available cable options were affordable and of excellent build quality. We even visited the factory to see their cable construction process in action. Nothing else we found, proprietary or commodity, could compare.

SmartVIO

One challenge for an interface standard aimed at FPGAs is accommodating the flexibility in I/O standard. Not 20 years ago, the dominant interface voltages were 5.0V and 3.3V. Today, devices often support ranges of interface voltages (e.g. 1.8V to 3.3V). FMC provides flexibility in I/O voltage, as communicated from the peripheral to the carrier, but a single voltage is provided for several dozens of pins, likely spanning multiple FPGA banks. Low-cost power-management ICs are available with 10mV resolution to affordably provide programmable power supplies to adapt to these (and future) peripherals.

SYZYGY peripherals would likely need to share a common FPGA bank, so we needed to provide for at least some degree of flexibility to allow compatible devices to share a common I/O voltage if they could. For this, we borrowed from FMC’s peripheral EEPROM and extended it to specify a range (multiple ranges, in fact) that could be supported by the peripheral. The carrier then selects a single I/O voltage that satisfies all peripherals (and the FPGA bank), if such a solution exists.

We also decided to employ the use of a small microcontroller instead of an EEPROM on the peripheral. Not only is this typically less expensive, but the embedded ADC allowed us to use a single pin to provide 16 geographical addresses rather than the two pins required by FMC to provide only 4 geographical addresses. The microcontroller can also be used to perform voltage sequencing on the peripheral, as necessary for some devices.

What’s Next?

A standard is legitimized through adoption. Our intent in creating a readily licensed standard was to encourage adoption by as many interested parties as possible. So far, there has been a lot of interest from carrier manufacturers but the chicken-and-egg problem exists until peripherals are widely available. Opal Kelly has several and we’re encouraged by Digilent’s adoption that more are on their way!

We would like semiconductor manufacturers such as Texas Instruments, Analog Devices, ON Semiconductor, and others to adopt SYZYGY for their data converter, image sensor, and other semiconductor evaluation boards. A common interface standard would extend the usefulness of these eval boards and allow them to interoperate with a broader range of carriers. This would improve the user experience for these eval boards and also provide a richer ecosystem for system integrators to assemble prototypes.

SYZYGY aims at a particular “sweet spot” in FPGA-peripheral interfaces that is long overdue. We are optimistic that carrier manufacturers, peripheral manufacturers, and consumers will find SYZYGY to be a Good Thing.